扇出型晶圆级封装(FOWLP)是一种新的异构集成技术,与传统的2.5D/3D IC结构相比,FOWLP可以在不使用昂贵的interposer情况下实现薄、高密度和低成本的IC封装。特别是近几年随着手机及各种智能穿戴设备的发展,消费者对超薄、超轻、高算力、多功能、低功耗的产品情有独钟。典型的2.5D/3D 封装很多都涉及到TSV(硅通孔)这一技术。虽然TSV技术也可以实现类似的功能,但是TSV成本高,良率不易保障。这时RDL成本低的优势就凸显了出来。

RDL技术再细分还分为RDL-first FOWLP和DIE-first FOWLP两种不同的工艺。与后者相比,RDL-first FOWLP的优势主要有:(1)高密度RDL线宽/空间;(2)高性能;(3)更大的芯片尺寸;(4)多芯片集成,(5)面板级应用。它也更适合应用于具有传统的倒装焊芯片Flip-chip的封装流程的OSAT代工行业。

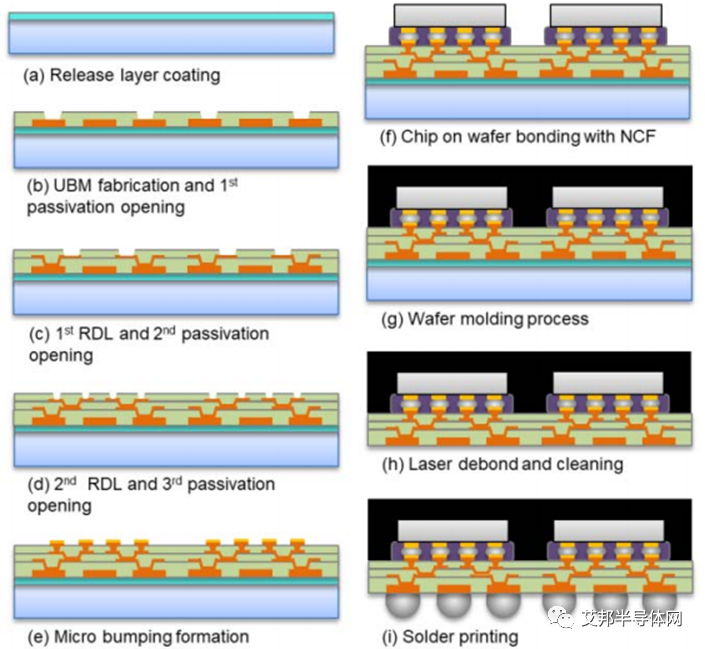

RDL first的FOWLP工艺如图1所示,首先(a)在1000um的玻璃基板上利用旋涂膜技术涂覆,烘烤成型后成型Ti/Cu种子层;(b)然后利用镀层工艺制备UBM(凸点下金属化层),接着再涂覆绝缘层/钝化层。这钝化层又具体包含的步骤有:旋涂,曝光,显影以及在200℃高温下后固化1小时以形成铜垫;(c)在生成第一层RDL的基础上,生成第二层开放钝化层;(d)形成第二层RDL层,并生成第三层开放钝化层;(e)形成微凸点;(f)将芯片贴装在RDL Wafer上,根据贴装精度不同,该步骤可采用热压键合(TCB)工艺,艾邦半导体公众号里对该工艺也有详细介绍;(g)晶圆塑封;(h)去除载板打磨露出RDL铜垫;(i)在RDL铜垫上完成贴球。

图1. RDL first FOWLP工艺步骤

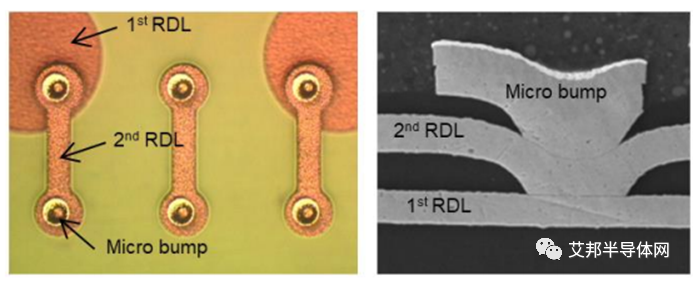

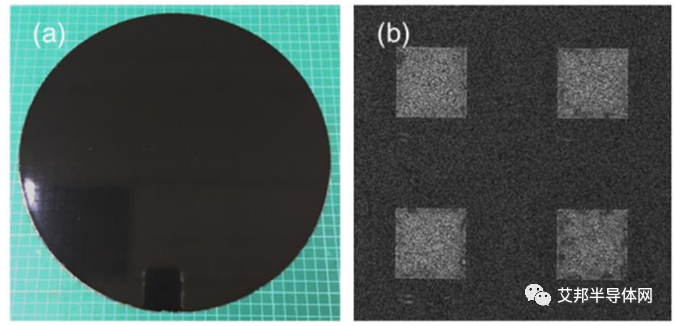

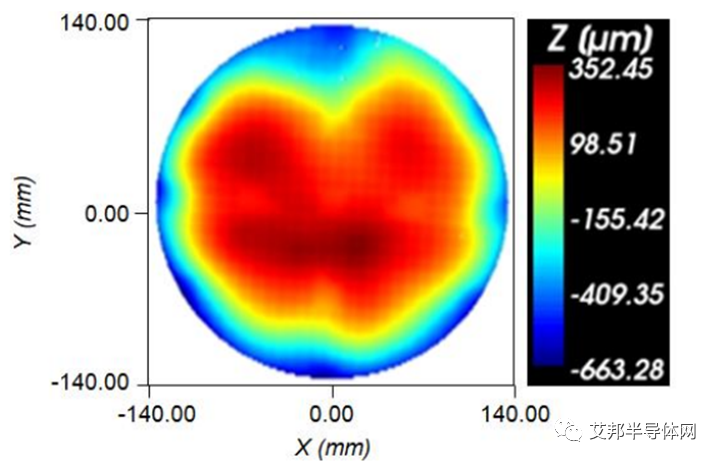

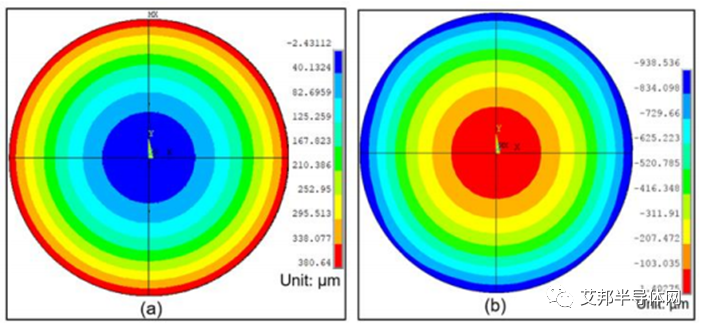

我们仔细看一下RDL层的剖面,如图2所示。晶圆塑封后的样子以及C-SAM气孔检测图如图3所示。塑封后的晶圆级翘曲如图4所示。

图2. RDL层剖面图

图3. 晶圆塑封后的样子以及C-SAM气孔检测图

图4. 晶圆塑封后的翘曲图

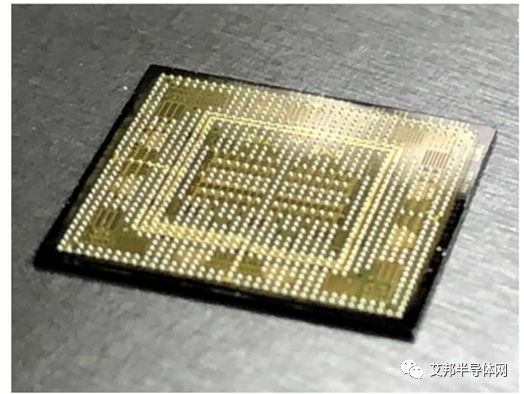

图5. 最终产品图

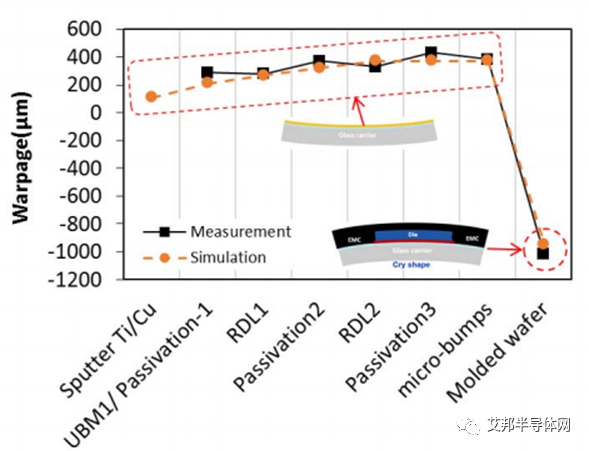

整个产品设计中翘曲预测至关重要,翘曲设计可以使用有限元分析法进行模拟,并于实物值进行对比。从图7可以看出,模拟值与实测值结果非常吻合。这说明在材料性质,尺寸等确定后,整个晶圆级别的翘曲是比较容易预测的。

图6. 左图为生成微凸点后的翘曲,右图为塑封后翘曲值

图7. 不同加工阶段晶圆翘曲模拟值与实测值曲线图

无论RDL 1st或是RDL Last 毋庸置疑的都归属于先进封装之列。我国在这方面有投入的封装厂并不多,从现有的报道来看主要玩家有长电、盛合晶微、豪微科技、奕斯伟、矽迈微等。在设备厂家上海微电的光刻机完全可以满足RDL的制备,也算是为我国后续RDL技术的普及奠定了良好的基础。如果您对RDL非常感兴趣,欢迎入群详聊。

参考文献:

An RDL-First Fan-out Wafer-level Package for Heterogeneous Integration Applications Yu-Min Lin…

原文始发于微信公众号(艾邦半导体网):先进封装之先制重布线层的扇出型晶圆级封装 RDL first Fan-out Wafer level Package