先进封装的创新优势为竞争日益激烈的市场带来前所未有的机遇。尤其是外形尺寸的改变和电性优势为客户提供优质方案,支持客户实现产品更高效的万物互联。随着5G成为主流,速度和效率大大提高人类生活质量,因此对依赖超低延迟的复杂应用需求越来越大。

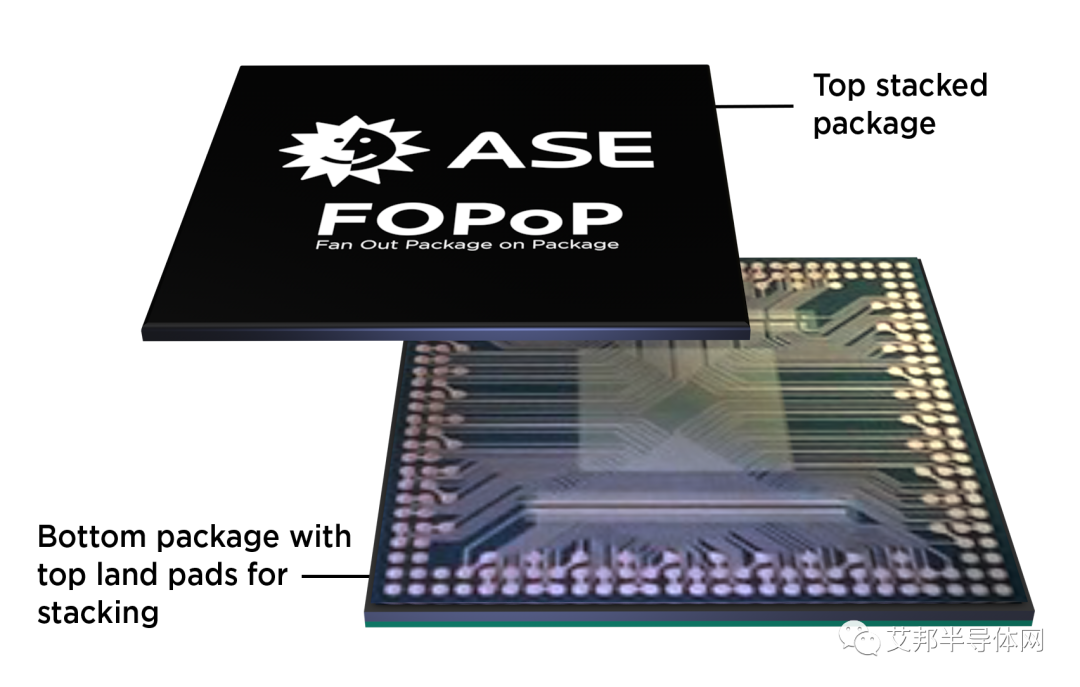

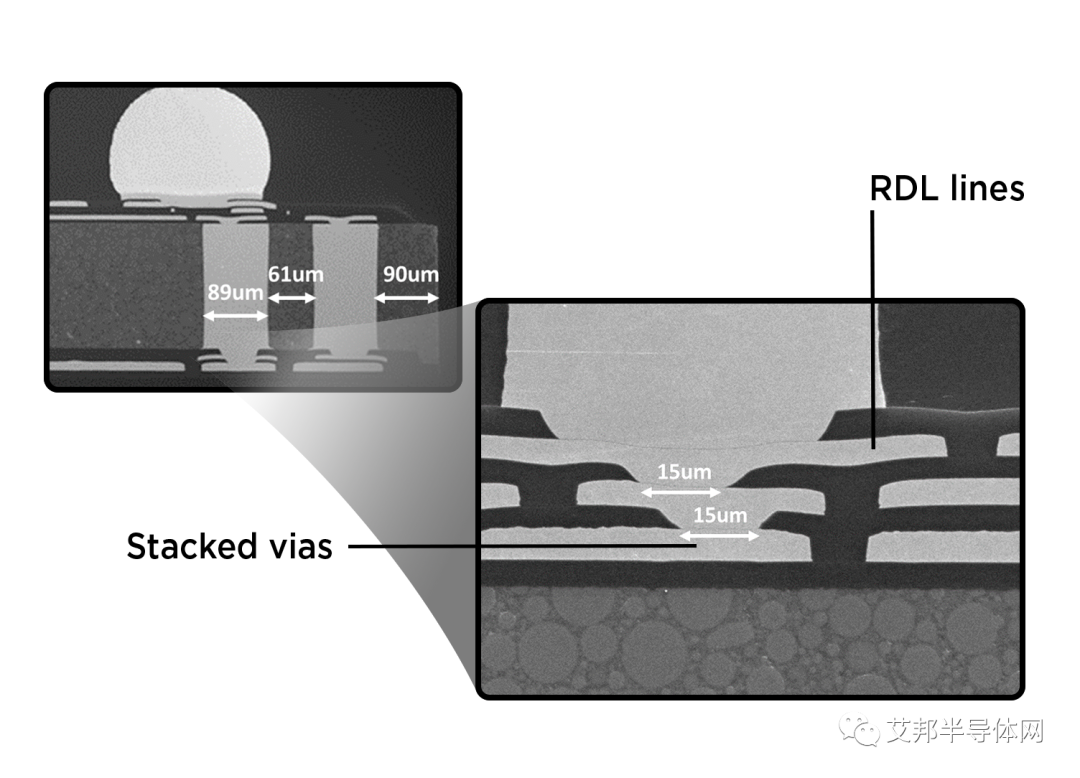

日月光FOPoP封装结构是最先进的垂直整合的集成技术,具备新型互连能力、增强驱动阻抗、堆栈通孔和启用垂直耦合等特性,延续未来长期技术蓝图的需求。

在移动装置应用中,FOPoP封装拥有更薄的封装尺寸,同时消除基板寄生电感,其高密度、无基板的特性实现更高的封装性能。FOPoP结构通过更精细的RDL线距,与基板相比,能提供更高的互连密度和集成度,更短距的互连长度,实现更好的电性性能以及更小、更轻薄的尺寸。FOPoP封装平台透过RDL多重布线层连结两侧裸晶来提高集成度和功能性,增强复杂且高性能需求。此外,也运用接脚侧 (land side)电容和近芯片深沟槽电容,满足先进节点的电源完整性要求。

在网络通讯应用中,FOPoP有助于实现下一代可插拔光收发器带宽从400G提高到800G,同时也利用共同封装光学组件(CPO)提供高度可行的集成解决方案。3D堆栈在光子集成电路(PIC)和控制器之间提供更短的互连,以达到更快的速度。FOPoP 3D堆栈是提升每尺寸更高带宽的解决方案,同时可以使小尺寸硅光子引擎(SiPh engine)和ASIC整合封装更容易,将是CPO关键技术。

FOPoP在移动装置市场的主要优势:

- 超低侧高的特质比基板型封装堆栈结构(Package-on-Package) 高度降低40%

- 优化电性效率提供先进硅节点电源优势

- 先进的材料能够在高温下获得良好的翘曲效果,呈现较好的表面黏装良率

- 与传统基板基电介质相比,使用扇出型PI(Fan Out Polyimide)可在更大的高频范围内保持稳定的介电常数(Dk)

- 新型制程和结构扩展产业蓝图,实现未来小芯片Chiplet的更多样异质和同质集成

FOPoP在网络市场的主要优势:

-

减少电气路径3倍,提高带宽密度8倍,引擎带宽扩展达到每单位4 Tbps

-

能效改善从25pJ/bit提高到5pJ/bit

-

10GHz以上优异损耗控制

-

提供激光器、光学器件和光纤站数组最先进的PIC、控制器芯片和特别预对准结构整合

-

通过使用被动对准,提供亚微米精度,提高光学耦合性能和封装效率

日月光研发副总洪志斌博士表示:“FOPoP在移动装置和网络通讯领域中克服几何架构的复杂性、实现电性效率且改变游戏规则,证明其具有极大的价值。凭借日月光丰富的经验和充足的技术基础能量,加上对研发的坚定承诺,日月光持续创造行业领先的封装解决方案,以满足客户需求。”

日月光销售与营销资深副总Yin Chang表示:“透过VIPack™垂直互连整合技术创新力的战略焦点,持续加快先进封装平台的发展步伐,确保我们的解决方案在市场上具有令人信服的性能。FOPoP是封装独创性的最佳范例,协助我们的客户保持领先,并将新一代产品迅速推向市场。”

原文始发于微信公众号(艾邦半导体网):日月光最先进扇出型堆栈封装(FOPoP)实现低延迟高带宽