我们在之前的文章中已经介绍过先进封装之面板级封装。(特别申明我们谈到的先进封装特别指高密度封装,线距线宽在2um~4um级别的)面板级与晶圆级封装的优势主要在于成本。而低成本又主要由载板的利用率以及加工速度(UPH)两方面体现。当然任何问题都有两方面,面板级封装的劣势是当前设备及材料供应链不够完善,工艺成熟度低,封测厂投入谨慎。那具体面板级封装与晶圆级封装的成本优势具体是怎么体现的呢?

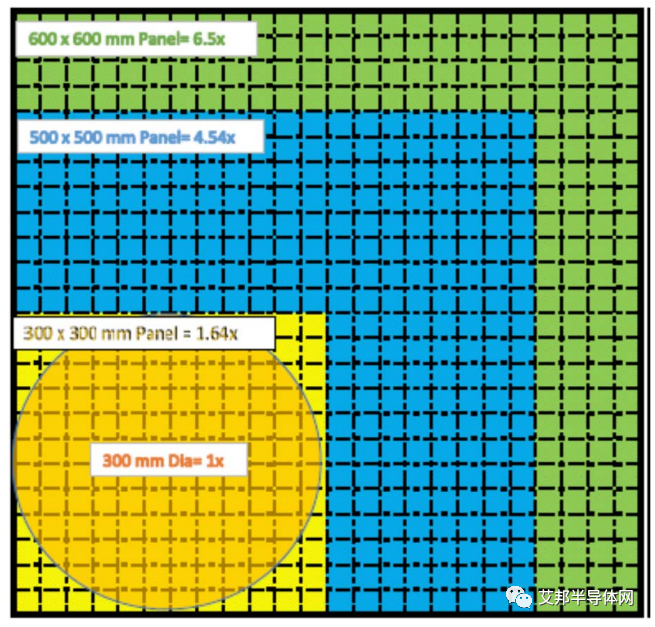

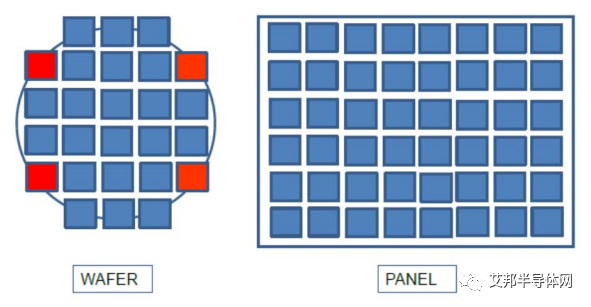

首先从图1可以看出,300x300mm的面板比12寸(300mm)的晶圆可以多容纳1.64倍的晶粒。而对比面板与晶圆两者的工艺,面板已经有供应商可以做到600mmx600mm,但是晶圆的大小由于当前供应链及主要玩家的扩大晶圆面积的积极性等原因,中长期内必将仍然停留在也是300mm。这也是为什么很多做显示面板的厂商想利用其在面板领域的积淀,突破半导体晶圆的尺寸,利用成本的优势打下一片天地。图2也可以看出在晶圆级封装上出现的Partial DIE(Edge缺陷DIE)将不会在面板级封装中出现。

图1. 不同面板级封装与12寸晶圆对比容纳的晶粒数量

图2. 晶圆级封装上出现的Partial DIE(Edge缺陷DIE)将不会在面板级封装中出现

从表1可以看出,利用面板级封装UPH基本是晶圆级封装的两倍以上。当然表中对比的是300mm晶圆与600mmx600mm的面板进行对比。虽然稍显在面积上欺负人,但是如果从载板工艺成熟度来看,300mm的晶圆与600mmx600mm的面板都是当前市场的主流。因此,这样的对比也有其合理性。相信,很多做面板级封装的厂家也是打着相同的算盘。

表1. 不同晶粒尺寸在Wafer级封装与面板级封装UPH的差异

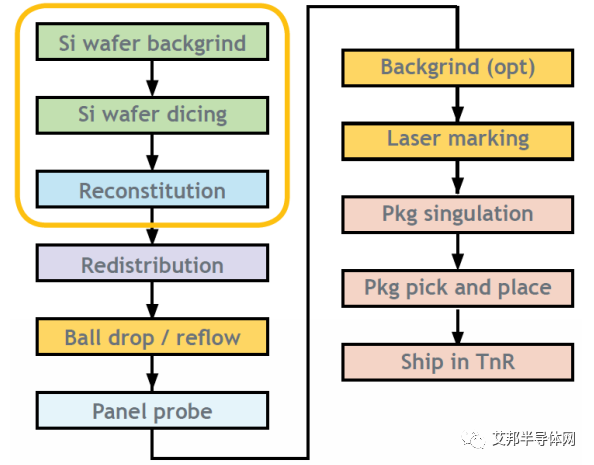

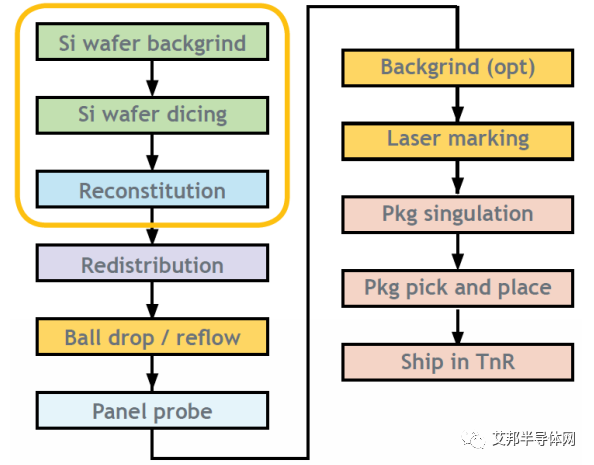

面板虽好,也不要轻视其工艺难度。今天继续谈谈面板级封装中的一些难点问题。既然先进封装,那势必涉及到一些光刻相关的工艺,特别针对DIE First的工艺,RDL都会根据DIE的位置利用光刻等工艺而生成。那么大致流程如图4所示,在将晶圆切割后的第三步即使将DIE都贴放在面板上,然后利用光刻,刻蚀等工艺加工RDL,也就是第四步Redistribution。所以面板级封装遇到的第一个难题就是DIE的贴装精度。

图4. STATSChipPac FlexLine™的eWLB扇出加工流程图

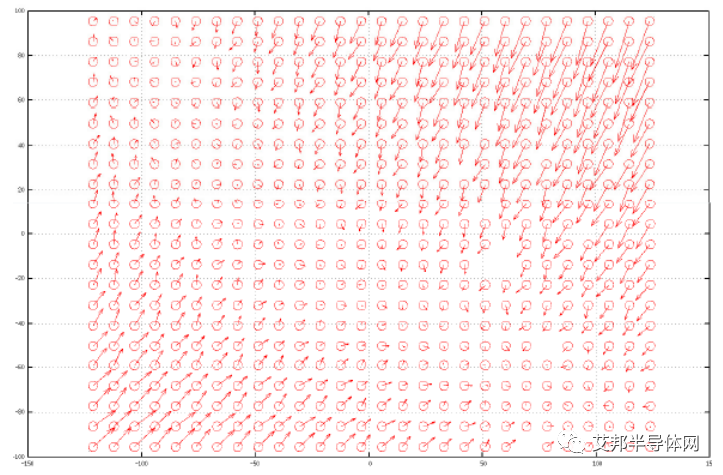

图5为DIE在面板上贴放后的位置矢量图,可以看出DIE在面板上歪歪扭扭,这对下一步的光刻等工艺将会带来巨大难度。例如,如果一定要在光刻机上进行对准,则光刻机的一半时间将会用于对准,使得光刻机的UPH降低一半以上。

图5. DIE在面板上位置矢量图,一个圆圈的半径为4微米 来源: Rudolph LSG Applications Center.

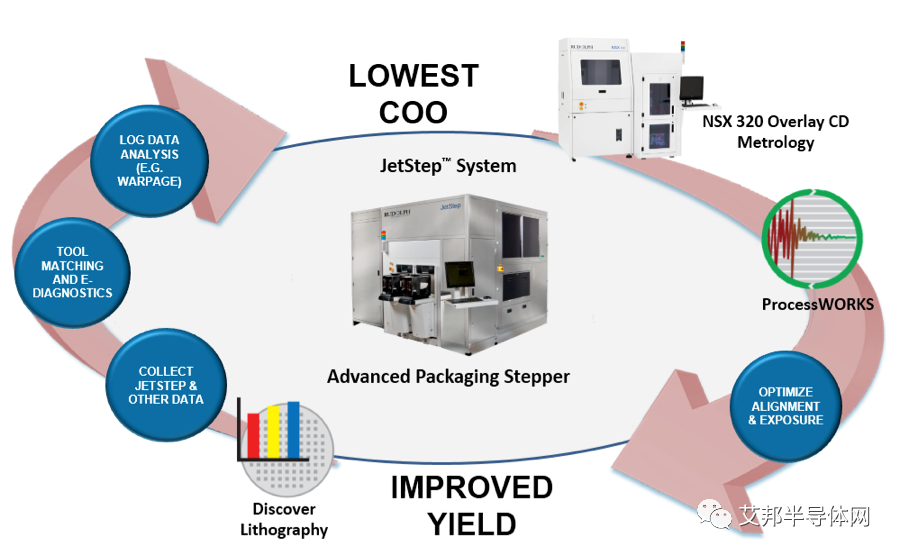

那如何解决这一问题呢?相信很多朋友已经想到了,提前对DIE的偏移量进行测量,将DIE的位置矢量图直接导入光刻机中。非常好,这也是鲁道夫技术公司(Rudolph Technologies)现与Nanometrics合并为Onto公司给出的答案。

图6. 鲁道夫技术公司的测量设备在光刻前进行测量并将校准数据输入到光刻机中

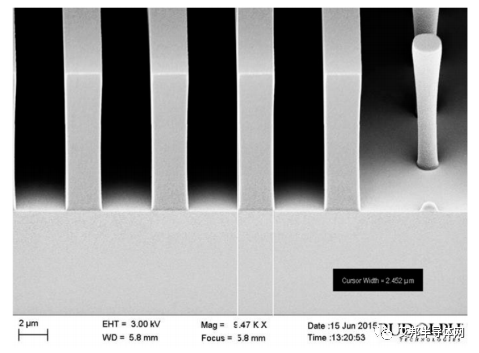

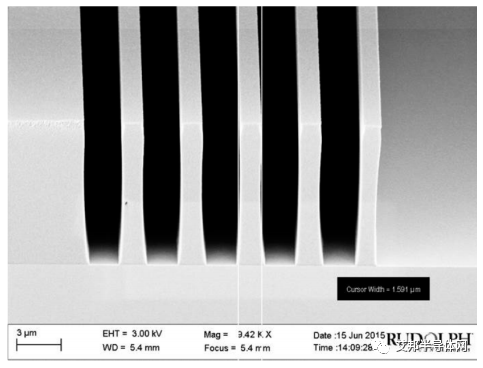

图7及图8为利用鲁道夫提前测量技术加工出产品的对准度。可以看出在2um及3um的维度上,对准一致,很好的为RDL中的光刻加工过程解决了由于晶粒贴装精度带来的位置偏差。

图7. 3um RDL结合处细节

图8. 2um RDL 结合处细节

最后再聊聊我国相关设备,由于量测设备涉及电学、光学、光声技术等多个技术领域,对设备制造企业的技术研发实力和跨领域技术资源整合能力有较高要求。国内设备厂商起步晚基础薄,国产设备仍有很大的突破空间。前道设备种类复杂,细分市场较多:其中膜厚量测技术门槛较低,集中度相对分散,为国内厂商进入检测设备的突破口。我国的东方晶源,科飞测、精测半导体、睿励科学仪器等都在积极布局,逐步参与。

参考文献:

1. Panel Level Advanced Packaging Roger McCleary, Philippe Cochet, Tom

2. Swarbrick, ChinTiong Sim, Gurvinder Singh, Yong Chang Bum, Andy

3. Advanced Packaging Lithography and Inspection solutions for next generation FOWLP-FOPLP processing Keith Best, Gurvinder Singh, Roger McCleary

4. High Resolution Patterning Technology to enable Panel Based Advanced Packaging Klaus Ruhmer, Philippe Cochet, Roger McCleary, Nelson Chen

5. 半导体行业深度分析:芯片良率重要保障,量检测设备国产替代潜力大 安信证券,马良,郭旺

原文始发于微信公众号(艾邦半导体网):先进封装之面板级封装(Panel Level Package,PLP)的对准问题