今天转载一篇大印蓝海科技的文章。

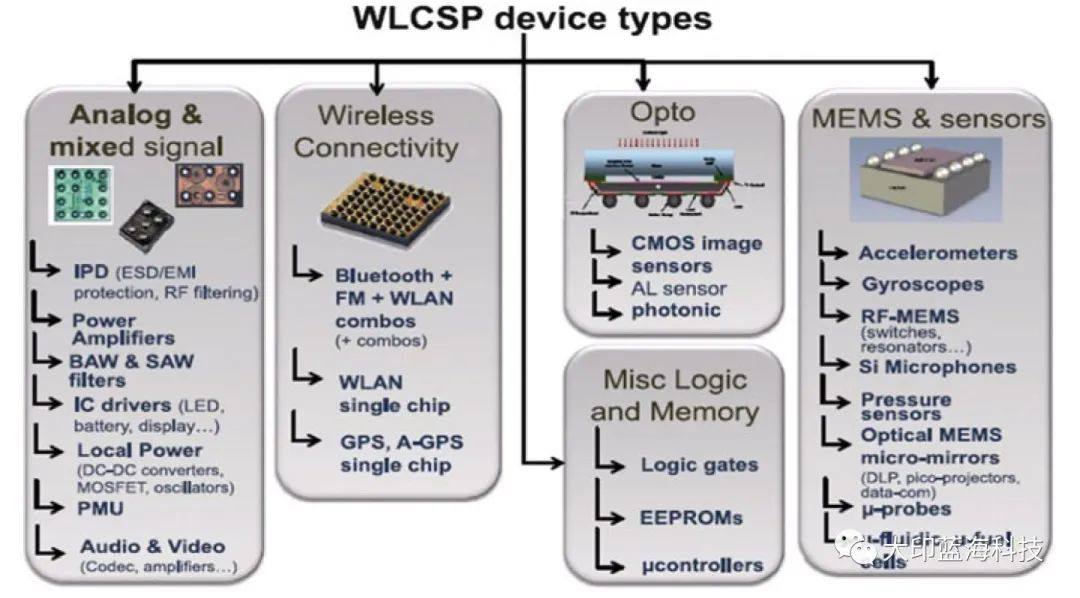

WLCSP(Wafer Level Chip Scale Packaging)即晶圆级芯片封装方式,不同于传统的芯片封装方式(先切割再封测,而封装后至少增加原芯片20%的体积),此种最新技术是先在整片晶圆上进行封装和测试,然后才切割成一个个的IC颗粒,因此封装后的体积即等同IC裸晶的原尺寸。在阅读本文之前欢迎识别二维码加入半导体先进封装产业链微信群;

WLCSP的封装方式,不仅明显地缩小内存模块尺寸,而符合行动装置对于机体空间的高密度需求;另一方面在效能的表现上,更提升了数据传输的速度与稳定性。

WLCSP的特性优点

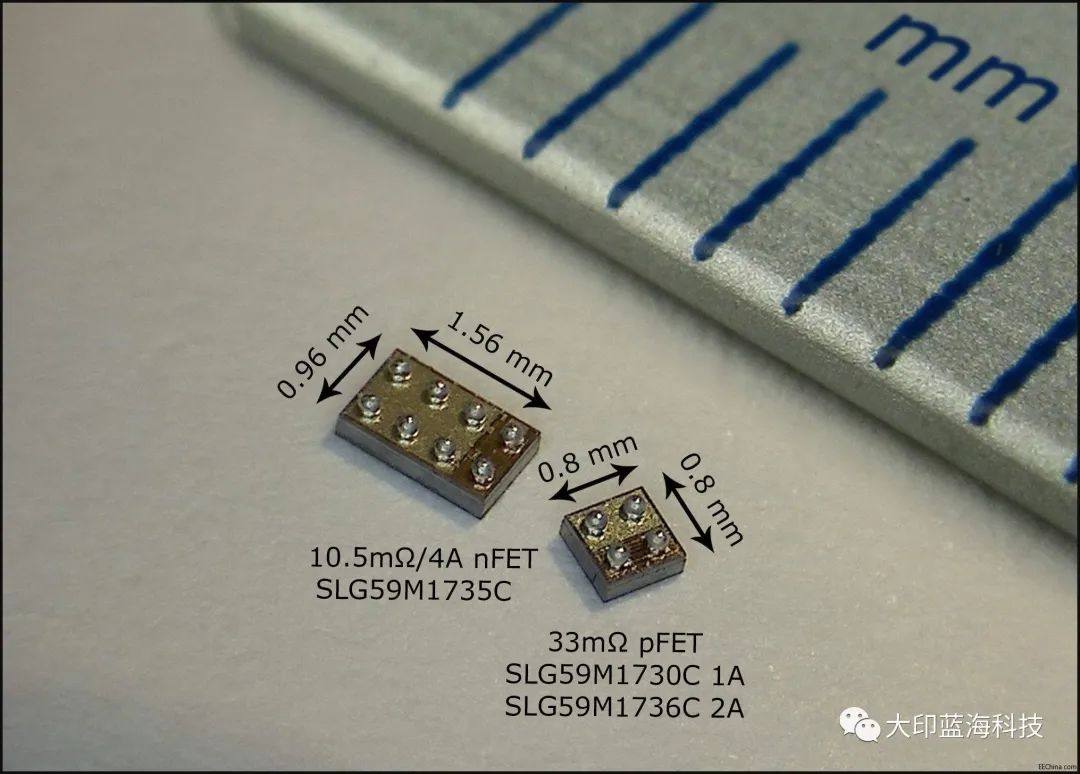

-原芯片尺寸最小封装方式:

WLCSP晶圆级芯片封装方式的最大特点便是有效地缩减封装体积,故可搭配于行动装置上而符合可携式产品轻薄短小的特性需求。

-数据传输路径短、稳定性高:

采用WLCSP封装时,由于电路布线的线路短且厚(标示A至B的黄线),故可有效增加数据传输的频寛减少电流耗损,也提升数据传输的稳定性。

散热特性佳

由于WLCSP少了传统密封的塑料或陶瓷包装,故IC芯片运算时的热能便能有效地发散,而不致增加主机体的温度,而此特点对于行动装置的散热问题助益极大。

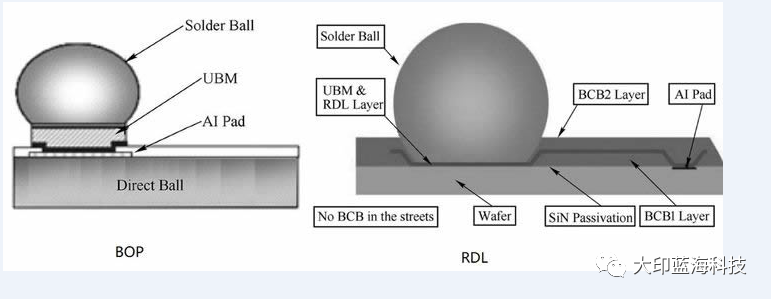

WLCSP可以被分成两种结构类型:直接BOP(bump On pad)和重新布线(RDL)。

BOP即锡球直接长在die的Al pad上,而有的时候,如果出现引出锡球的pad靠的较近,不方便出球,则用重新布线(RDL)将solder ball引到旁边。

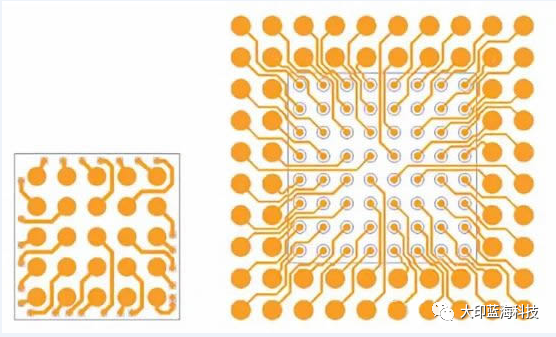

最早的WLCSP是Fan-In,bump全部长在die上,而die和pad的连接主要就是靠RDL的metal line,封装后的IC几乎和die面积接近。Fan-out,bump可以长到die外面,封装后IC也较die面积大(1.2倍)。

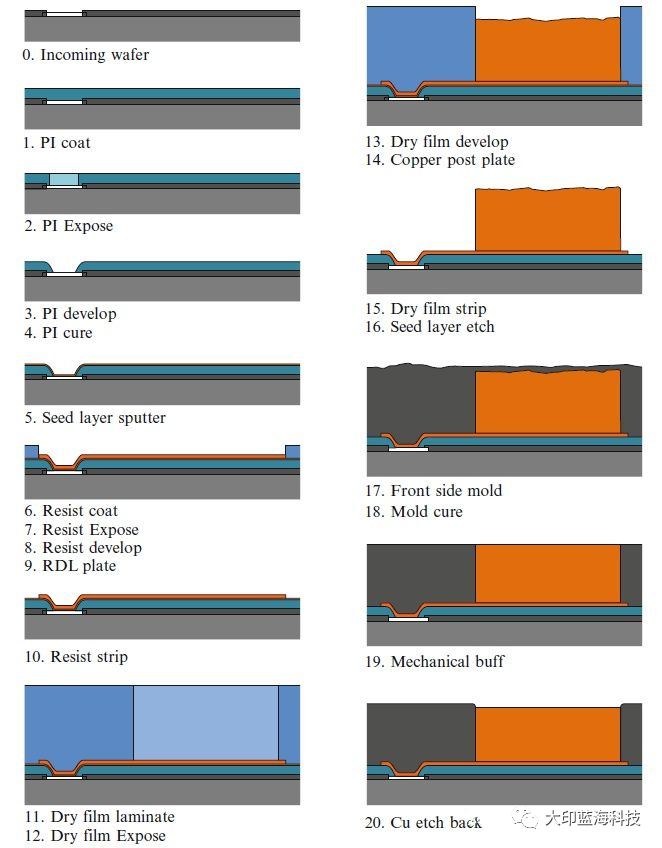

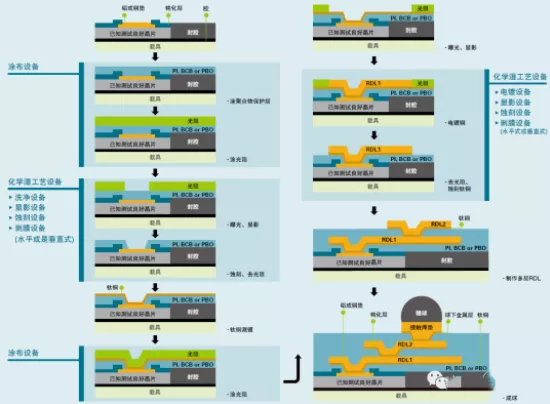

Fan-in: 如下流程为Fan-in的RDL制作过程。

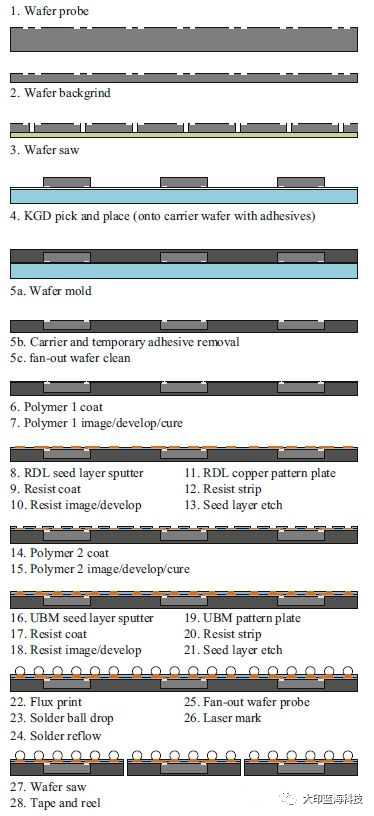

Fan-Out: 先将die从晶圆上切割下来,倒置粘在载板上(Carrier)。此时载板和die粘合起来形成了一个新的wafer,叫做重组晶圆(Reconstituted Wafer)。在重组晶圆中,再曝光长RDL。

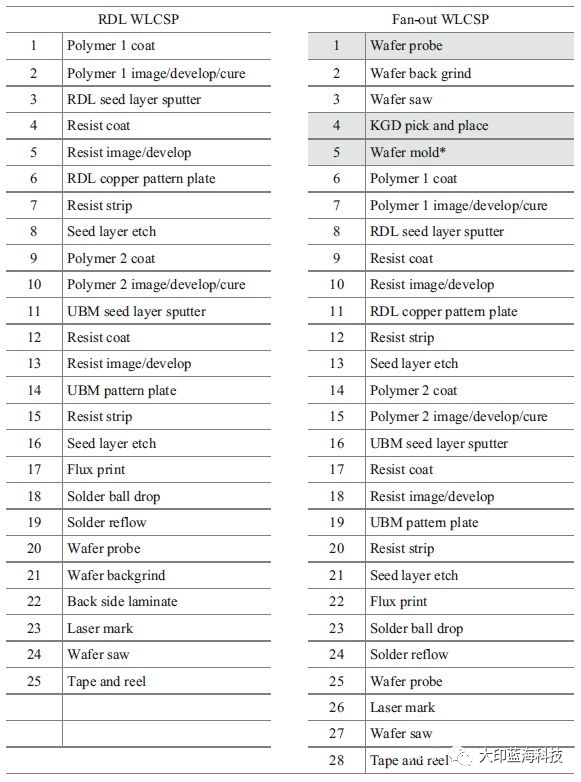

Fan-in和Fan-out 对比如下,从流程上看,Fan-out除了重组晶圆外,其他步骤与Fan-in RDL基本一致。

延展阅读

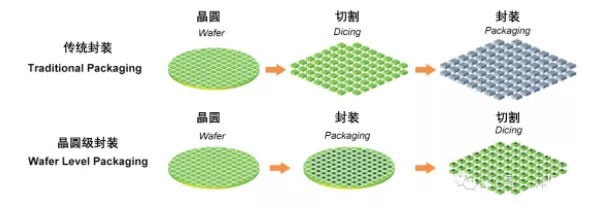

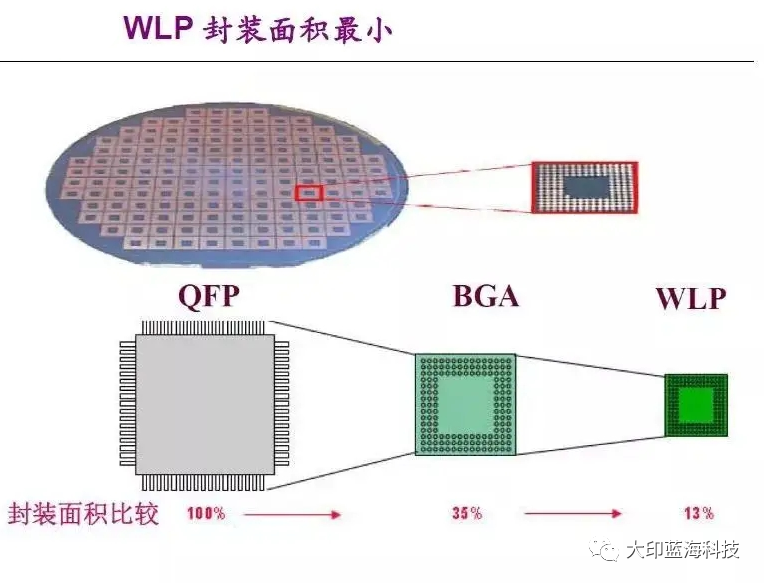

一、WLP晶圆级封装VS传统封装

在传统晶圆封装中,是将成品晶圆切割成单个芯片,然后再进行黏合封装。不同于传统封装工艺,晶圆级封装是在芯片还在晶圆上的时候就对芯片进行封装,保护层可以黏接在晶圆的顶部或底部,然后连接电路,再将晶圆切成单个芯片。

相比于传统封装,晶圆级封装具有以下优点:

1、封装尺寸小

由于没有引线、键合和塑胶工艺,封装无需向芯片外扩展,使得WLP的封装尺寸几乎等于芯片尺寸。

2、高传输速度

与传统金属引线产品相比,WLP一般有较短的连接线路,在高效能要求如高频下,会有较好的表现。

3、高密度连接

WLP可运用数组式连接,芯片和电路板之间连接不限制于芯片四周,提高单位面积的连接密度。

4、生产周期短

WLP从芯片制造到、封装到成品的整个过程中,中间环节大大减少,生产效率高,周期缩短很多。

5、工艺成本低

WLP是在硅片层面上完成封装测试的,以批量化的生产方式达到成本最小化的目标。WLP的成本取决于每个硅片上合格芯片的数量,芯片设计尺寸减小和硅片尺寸增大的发展趋势使得单个器件封装的成本相应地减少。WLP可充分利用晶圆制造设备,生产设施费用低。

二、晶圆级封装的工艺流程

WLP工艺流程

晶圆级封装工艺流程如图所示:

1、涂覆第一层聚合物薄膜,以加强芯片的钝化层,起到应力缓冲的作用。聚合物种类有光敏聚酰亚胺(PI)、苯并环丁烯(BCB)、聚苯并恶唑(PBO)。

2、重布线层(RDL)是对芯片的铝/铜焊区位置重新布局,使新焊区满足对焊料球最小间距的要求,并使新焊区按照阵列排布。光刻胶作为选择性电镀的模板以规划RDL的线路图形,最后湿法蚀刻去除光刻胶和溅射层。

3、涂覆第二层聚合物薄膜,是圆片表面平坦化并保护RDL层。在第二层聚合物薄膜光刻出新焊区位置。

4、凸点下金属层(UBM)采用和RDL一样的工艺流程制作。

5、植球。焊膏和焊料球通过掩膜板进行准确定位,将焊料球放置于UBM上,放入回流炉中,焊料经回流融化与UBM形成良好的浸润结合,达到良好的焊接效果。

三、晶圆级封装的发展趋势

随着电子产品不断升级换代,智能手机、5G、AI等新兴市场对封装技术提出了更高要求,使得封装技术朝着高度集成、三维、超细节距互连等方向发展。晶圆级封装技术可以减小芯片尺寸、布线长度、焊球间距等,因此可以提高集成电路的集成度、处理器的速度等,降低功耗,提高可靠性,顺应了电子产品日益轻薄短小、低成本的发展要需求。

晶圆级封装技术要不断降低成本,提高可靠性水平,扩大在大型IC方面的应用:

1、通过减少WLP的层数降低工艺成本,缩短工艺时间,主要是针对I/O少、芯片尺寸小的产品。

2、通过新材料应用提高WLP的性能和可靠度。主要针对I/O多、芯片尺寸大的产品。

原文始发于微信公众号(艾邦半导体网):WLCSP晶圆级芯片封装技术